RTL 論理合成(性能予測)

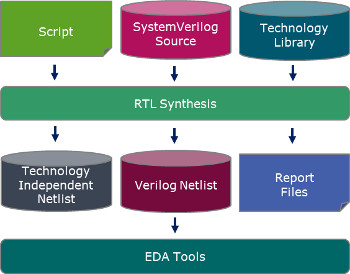

RTL 論理合成は設計の初期段階において、物理設計後の実装状況を正確に見積もる為の機能を提供します。RTL 論理合成機能はユーザ指定のライブラリーを使用してVerilog ネットリストを生成します。RTL 論理合成は業界標準のテクノロジーライブラリーをサポートしています。生成されたネットリストを使用して他のEDAツールにより各種の解析を正確に行なう事が出来ます。

論理合成は、一般に、複雑な変換過程を得てネットリストを生成しますが、大きく分けると次の四工程から成ります:

① コンパイル(シンタックスチェック、エラボレーション)

② テクノロジー独立論理合成

③ 論理の最適化

④ マッピング

コンパイルのフェーズは、入力であるRTL記述が言語仕様に遵守しているかを確認する過程です。合成フェーズは、RTL記述をブーリアン論理に変換をする過程です。最適化は冗長な論理を除去する目的を持ちます。マッピングは、最適化された論理をライブラリーセルで表現する過程です。目的に合わせて論理合成を使用する事により物理設計時に遭遇するであろう問題を未然に防ぐ事が出来ます。